��20 �����(l��i)���S����(sh��)��ͨ�ŵĿ��ٰl(f��)չ����̖(h��o)�·�е�ģ��(sh��)�D(zhu��n)�Q����ADC��������Խ��(l��i)Խ��Ҫ�������ٌ���ADC �ɏV����(y��ng)�����l(w��i)�ǡ����_(d��)����ӑ�(zh��n)����(sh��)��ʾ������ͨ�ŵȽ��ՙC(j��)�I(l��ng)���y(t��ng)����8λADC �mȻ�Y(ji��)��(g��u)�D(zhu��n)�Q�ٶȿ죬���·Ҏ(gu��)ģ�S�ֱ��ʶ�׃��n ��2n ָ��(sh��)���L(zh��ng)[3��4]�����Ĵ��ۯB/ ��ֵ�ͽY(ji��)��(g��u)ADC ���б��^���Ĕ�(sh��)������ͨ�^(gu��)�ۯB�Ͳ�ֵ�D(zhu��n)�Q��(l��i)��ͣ��D(zhu��n)�Q�����ஔ(d��ng)������(g��)���нY(ji��)��(g��u)��Ȼ������ʹ�����p�O��ˇ���ۯB�Y(ji��)��(g��u)�·��Ȼ�ܵ��O(sh��)��ʧ���Ӱ푡����\(y��n)���ǣ�ǰ�˔�(sh��)��У��(zh��n)�㷨�����Á�(l��i)�����O(sh��)��ʧ�䌦(du��)�·���ܵ�Ӱ푡�

оƬ��ُ(g��u)�W(w��ng)��ע�����χ�(gu��)��(n��i)���ڙ�(qu��n)IC�����̬F(xi��n)؛�YԴ��оƬ��(k��)�挍(sh��)�r(sh��)��ԃ���ИI(y��)�r(ji��)���������ُ(g��u)����ICоƬ����(gu��)��(n��i)���I(y��)оƬ��ُ(g��u)ƽ�_(t��i)��

�ۯB/ ��ֵ��ADC ǰ�˔�(sh��)��У��(zh��n)�㷨���Լm���O(sh��)��ʧ�䣬��У��(zh��n)��(d��ng)�B(t��i)�r(sh��)状���(d��ng)�`����Ҫ�ܴ�ijɱ�����ˣ��ۯB/ ��ֵ��ADC ǰ��һ����ø��ٌ����ɘӱ����·��S/H�����ɘӕr(sh��)状���(d��ng)��Ӱ푿�����Ч���͡����������һ�N����0�Ļ��A(ch��).18 ��m BiCMOS���ú�(ji��n)�εĔ�(sh��)��У��(zh��n)�㷨�����Դ���·�������`���ʧ���`��·ģ�M�͌�(sh��)�H�y(c��)ԇ��������ͨ�^(gu��)��(sh��)��У��(zh��n)�ɘӱ����·�����ʧ���`���ADC ��(d��ng)�B(t��i)���ܿ����10 dB ���ϡ�

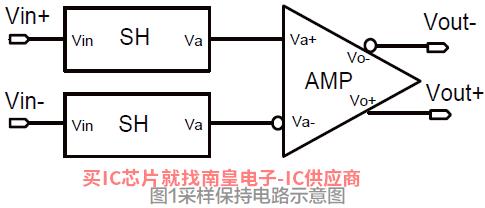

1 �ɘӱ����·�O(sh��)Ӌ(j��)

�ɘӱ����·�ɘ����_(d��)��2GSPS������S/H �·�����_(k��i)�h(hu��n)�Y(ji��)��(g��u)��S/H �·ϵ�y(t��ng)�ɲɘӱ��ֵȼ�(j��)��SH���·�ͷŴ���(q��)��(d��ng)��(j��)��AMP���·�M�ɡ�

�D9 Fin=484MHz, Fs=2GSPS��ADC��SFDR

5 �Y(ji��)Փ

��������Ļ���0.18 ��m BiCMOS ��ˇ�O(sh��)Ӌ(j��)�ĸ��ٌ����ɘӱ����·���ɹ���(y��ng)����8 �����ۯB/ ��ֵA(ch��)DC �У�������ADC ��(d��ng)�B(t��i)���ܺ�ݔ�뎧�����ɘӱ����·�_(k��i)�h(hu��n)�Y(ji��)��(g��u)�������D(zhu��n)�QAzoteq�������ʳ��^(gu��)2GSPS�����������ʧ�┵(sh��)��У��(zh��n)�㷨����·���o�B(t��i)�̈́�(d��ng)�B(t��i)���ܡ�ADC �·ԇ�(y��n)�Y(ji��)����(y��u)�����f(shu��)���O(sh��)Ӌ(j��)�ĸ��ٌ����ɘӱ����·�M��Ҫ��

�����īI(xi��n)��

[1] YU J S, ZHANG R T,ZHANG Z P,et al.A digital calibration technique for an ultra high-speed wide-bandwidth folding and interpolating analog-to-digital converter in 0.18-��m CMOS technology[J]. Journal of Semiconductors,2011,32(1):977.

[2] FLYNN M P,SHEAHAN B.A 400-Msample/s,6-b CMOS Folding and Interpolating ADC[J].IEEE Journal of Solid- State Circuit,1998,33(12):1932.

[3] LEE D, SONG J,SHIN J,et al.Design of a 1.8V 8-bit 500MSPS Folding-Interpolation CMOS A/D Converter with a Folder Averaging Technique[C].18th European Conference on Circuit Theory Design,2007:356.

[4] ALI A M, MORGAN A,DILLON C,et al.A 16 b 250MS/s IF-sampling pipelined A/D converter with background calibration[C].IEEE International Solid-State Circuit Conference Digest of Technical Papers,2010:292.

[5] CHU M, JACOB P,KIM J-W,LeRoy M R,et al.A 40Gs/s Time Interleaved ADC Using SiGe BiCMOS Technology[J]. IEEE Jouurnal of Solid-State Circuit,2010,45(2):380.

(���ā�(l��i)Դ��IC2022��5�£������s־

- ��о�@��3000�f(w��n)��Ԫ���������аl(f��)GaNоƬ

- R&S�y�ָ�ͨ��NAB 2022չ��(hu��)����ʾ�����֙C(j��)�Ķ˵���5G��ý�wֱ��

- �����Ƽ��c����Teradyne����ETS�O(sh��)�� �˽�댧(d��o)�w܇(ch��)���Ј�(ch��ng)څ��(sh��)

- ��ɹ����g(sh��)Bһ݆��(sh��)�|Ԫ���Y����ToFоƬ�͂��������a(ch��n)���

- NVIDIA�V�������A(y��)�������ܕ�(hu��)Ӱ�����

- �W�ƹⱻጷŞ������ �I(y��ng)������

- ���A�����Г��ƿ���С���ܵõ�ʲô��

- Software R��publique2022�����܇(ch��)չ�ϳ��F(xi��n)�˰�ȫ���ܵ�늄�(d��ng)��܇(ch��)���վ

- ȫ���ׄ�(chu��ng)��Apollo���^(gu��)1500�f(w��n)����܇(ch��)�d�z���^

- ����Դ��׃�ﱳ��

- ��(li��n)�W(w��ng)���ܼҾӰ�ȫ�ģ�Մ��(li��n)�W(w��ng)���ܼҾӰ�ȫ

- �������_(k��i)ʼʹ��5G�A����ܕ�(hu��)�и���ļ��g(sh��)�C(j��)��(hu��)