�O���l(f��)���������賿�O�������l(f��)��������� ��M1 Ultra��оƬ��

оƬ��ُ�W(w��ng)��ע�����χ���(n��i)���ڙ�(qu��n)IC�����̬F(xi��n)؛�YԴ��оƬ��挍�r��ԃ���ИI(y��)�r���������ُ����ICоƬ������(n��i)���I(y��)оƬ��ُƽ�_��

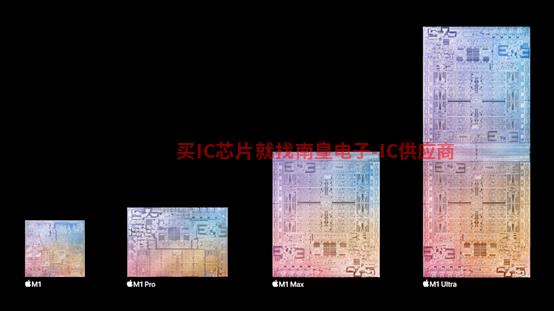

�O���ڕ��h������ M1 Ultra оƬ�����S������ą���(sh��)����1140�|�w���w�ܣ�20��CPU��16 �����܃�(n��i)�˺� 4 ��Ч��(n��i)��)�����64��GPU��32����(j��ng)�W(w��ng)�j(lu��)���棻2.5TB/s��(sh��)��(j��)��ݔ����8000GB/s��(n��i)�控�����128GB�y(t��ng)һ��(n��i)�档

M1 Ultra �� Apple оƬ����һ���Α�Ҏ(gu��)�t׃���ߌ��ٴ����@ PC �ИI(y��)��ͨ�^�ɂ�M1 Max оƬ���҂��� UltraFusion �҂������B�ӷ��b�Y(ji��)��(g��u) Apple оƬ�Uչ��ǰ��δ�е��¸߶ȡ�

�O����Ӳ�����g(sh��)Espressif������������Johny Srouji��ʾ:�{����������CPU������� GPU����(j��ng)���������y�����ţ�ProRes Ӳ�����ٺʹ����y(t��ng)һ��(n��i)�棬M1 Ultra ������M�ɞ�������������Ă���Ӌ��CоƬ��

�O����Ultra Fushion�ܘ�(g��u)������֪��Ҫ����������оƬ������Ҫ�ѷe������·�;��w�ܡ���ˇԽ���M��ͬһ�^(q��)��ľ��w��Խ�࣬оƬ��������Խ�ߣ��@Ҳ���˂�������M��ˇ��ԭ��֮һ��

Ȼ������Ŀǰ�Ĺ�ˇ�ͼ��g(sh��)�l���£�������w���^�࣬���ʌ����ͣ����ʌ����ͣ�ÿ��оƬ��׃�÷dz����F����ô������ڽ��ͳɱ���ǰ�������쳬Խ�O��оƬ�أ�

�����O��������M1 Maxͨ�^�[�������g��оƬ���Bģ�KUltraFushion�ܘ�(g��u)���ɉKоƬ��ƴ�Dһ�Ӻ϶���һ��

�O���ġ�UltraFushion���䌍����Die to Die Connection����оƬ�O(sh��)Ӌ�У�ͬһ���b��package��ʹ�ö�����Ƭ��silicon���������O(sh��)Ӌ�˘O����ٵĻ�(li��n)ͨ����ʹ�@�ɂ���Ƭ�܉���ͬһ��оƬһ�ӹ�����

UltraFusionʹ����1�f�lDTD���_2���B��.5TB/s���Ļ�(li��n)�ٶȘO�ߣ��ܺĘO�ͣ�������ǎKdie(li��n)�ϰ��b�����ʵ��������h(yu��n)���ڳ�����оƬ�����DTDҲ���J(r��n)����δ��оƬ���ܰl(f��)չ?ji��)�����ĵ�·�?/p>

ֵ��һ����ǣ�M1 Max��СоƬ����A(ch��)(Chiplet)���O(sh��)Ӌ�У�оƬģ�K�ѯB����оƬ(MCM)����2-tileʹ���Ҏ(gu��)��CPU��GPU��NPU�ă�(n��i)�控������(n��i)������������2xM1 Max��Ҏ(gu��)��

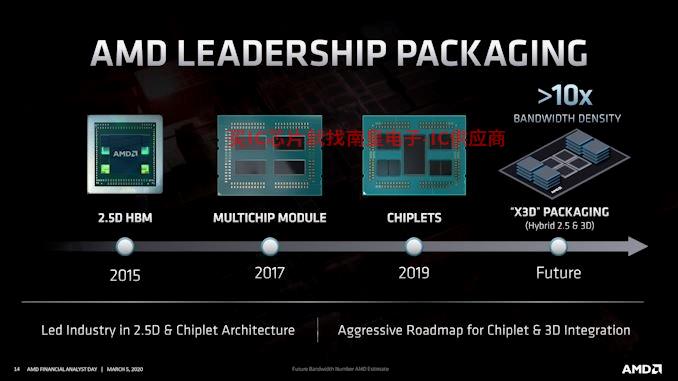

�c�A���оƬ�B�ӌ�������һ����(d��ng)Ȼ���O������Ψһһ�l·��AMD ���� 2017 ���������MCM ������ 2019 ��������Chiplet �O(sh��)Ӌ��δ���İl(f��)չڅ�����Mһ����߶ѯB���������F(xi��n)���^�� 3D �ѯB��Ҳ�����f�����H�H�� 2D ���ϔUչ��ҲҪ��ֱ����Uչ��

�A�麣˼�ڇ���(n��i)��I(y��)Ҳ��ͬ�ӵ��뷨��2021��5�£��A�鹫�_���pо�B�ӌ���������ʾ14nm���g(sh��)���_7nm�@����Ϣһ����������ȫ���������˟��h��������ȫ������P(gu��n)ע�������v14nm�c7nm����֮�g����Ҫ�^(q��)�e��оƬ��e��ͬ��7nm���w�ܔ�(sh��)���������ӣ�������Ȼ����ߡ�

�����ܮa(ch��n)ƷChiplet�@�l·�ߵ�֪ͨ���Ñ�@���Ͻ�ʺ��DZ�ʾ�@�wM1Ultra�@���O��Ұ�ĵ��Mһ�����m(x��)����������е��O��Ҳ�D(zhu��n)����Chiplet��ˣ��@���������ܮa(ch��n)Ʒ���ܕ���δ�������M�I(l��ng)������Chiplet�@�l·�����ߵ�ͨ��Ŀǰ��оƬ�M�ϯB���я���Փ�D(zhu��n)׃?y��u)�F(xi��n)������оƬ���b�ĽǶȁ�������2�_ʼ.5D���b����3D���b��о��(Chiplet) �ṩ������ܺ�����`���ԡ��_�e늣�Ӣ�ؠ������ǣ�AMDʮ�ҹ�˾�ѽ�(j��ng)��ȡ�Єӣ���ͬ����UCIe(li��n)�ˡ�(Ԕ��:Ӣ�ؠ���AMD��Arm�ȾŴ���I(y��)����UCle�_�Ř�(bi��o)��(zh��n)�����MChiplet�l(f��)չ��

UCIe(li��n)�˵ij����nj�СоƬ������_�Ż�(li��n)�Įa(ch��n)�I(y��)�l(f��)չ���B(t��i)����ͬ�Ŀ͑�ͨ�^���NСоƬ�a(ch��n)Ʒ�M����������

δ������Chiplet����ģʽ��оƬ����һ����������(g��u)ϵ�y(t��ng)�����Ԏ���������`���Ժ��µęC����

оԭ�ɷ�����˾��(chu��ng)ʼ�ˡ������L�濂�ô���������ʾ�������ИI(y��)���ԣ�Chiplet�ژ�(bi��o)��(zh��n)�����B(t��i)�����ϣ�Chiplet�������µĿɻ������M������(li��n)�f(xi��)�h��ܛ�����B(t��i)ϵ�y(t��ng)����оƬ����Ͱ��b�����˶�оƬģ�K (Multi-Chip Module��MCM) �I(y��)��(w��)��Chiplet���������h(yu��n)����ASIC������߾��A�S�ͷ��b�S�����a(ch��n)�������ʣ��댧(d��o)�wIP������Chiplet����(y��ng)�̣���������IP�����оƬ�O(sh��)Ӌ�������˴�Ҏ(gu��)ģоƬ�O(sh��)Ӌ���T����

�������h����(n��i)��I(y��)�^�m(x��)���MChiplet���a(ch��n)��2.5D/3D�_�l(f��)��y���g(sh��)��

- ��̩��Ͷ�Y �_PCB�S�����M

- AMD Zen4�J��7000ȫ���ع�:16����5.7GHzһ�w�_�죡

- ��ͨ:�c�_�e늡����ǃɴA�S�������M��ˇ������(zh��n)��

- VIAVI����棺2021������635������5G�ij��У�5G���wȫ��1947������

- BOE�����|����2022��һ����:�I�ճ�500�|Ԫ ���|(zh��)���l(f��)չ��(w��n)�����M

- ����Ӌ���ڵ���Ͷ�Y2000�|��Ԫ����11��оƬ�S

- Google���_ԴPDK������ʲô���Lԇ�@�ӵ����r�棡

- BaaS�Ї��^(q��)�K�?zh��n)Ј��?gu��)ģ����ͻ�ƣ��Ј�����ٴΰl(f��)��׃��BaaS2021��l(f��)���Ј����~

- ���_����Ƴ���(f��)���(q��)��ܛ�����ӿ�늄���܇늳ع���ϵ�y(t��ng)�İl(f��)չ

- �ʿ�RGB DDR4���l��4266MHz!����(n��i)��(n��i)����¸߶�

- Inuitive �c Arteris IP ߅���O(sh��)����� �ṩ��һ��ҕ�X̎�����g(sh��)

- ʩ�͵�늙C��һ��늙C������ ��(chu��ng)��ɳ��m(x��)����ȫ�Ŀ͑��w�