оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

ÿ��ׂ��¾͕����F���µ���ӮaƷ��������һ�����M��оƬ��̎����������ͨ����С�������ܣ����H�\���ٶȸ��죬�������࣬���Ҹ����ܡ�

�M�딵�֕r�����҂���������̫ꖕ��������O�䌢�^�m���¡���Ļ���̎����e�O�о��댧�w���g·���D���Դ_�����O���������һ��оƬ�ʂ�;w��

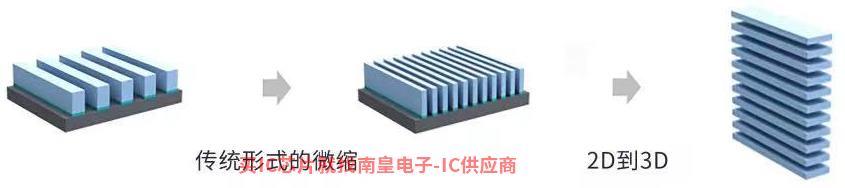

���Lһ�Εr�g�ԁ���оƬ���M����ͨ�^�sС���w�ܵijߴ�팍�F�ģ��@�Ӹ���ľ��w�ܾͿ����ھ��A�����죬�Ķ�ʹ���w�ܵĔ���ÿ12-24���·�һ�������@���DZ�����֪��Ħ�����ɡ�����������˸��ϕr���IJ����������ИI�M�����~/��k���B�����;��w�ܲ��ϡ����D�η��������S(3)���T���ش���D)�ܘ���

�_�l3D�S����ȵ����ӣ��Y����׃���������µ�����������ѽ��뵽��3D�ܘ���Ҫ�ĸ����ϸ�׃�O���OӋ����Ҫ�µIJ��ϡ��µij��e���g�̷������ڱ����У��҂���������댧�w�ИI�Č��FD�����^���е���Ҫ��̱���

�ʂ��A�Σ�Inphi����ƽ�湤ˇ

����һ�������·�����һ�����S���}��ȡһ��ƽ̹�Ĺ�Ƭ�������N�Y�������ڱ��棬���Ì����B�ӡ��@��ͨ�^���e�ӌӲ��ϣ����ù�̼��g�M�ЈD��̎�������ڱ�¶�^���g�̱�Ҫ�����ԁ���ɵġ��@��������ӹ��I��һ����ͻ�ơ�

�S�����g����IJ���lչ����Ҫ�ڸ��o���Ŀ��g�н���������·��֧�ָ�С�ĽY�����^ȥ����ֱ�ӵ��^��׃��Խ��Խ���s��

�S������2D�S���Y���ɱ������ӺͶ��Sƽ���s�Ŀ��з�������u�ݽߣ�3D�Y��׃��Խ��Խ��������������ʮ����ǰ���댧�w�ИI���_ʼ�_�l���ڵ��x�����g�̑��ã���֧��3D�İ��b������ʧ�Դ惦���������w�ܱ��������g�����Uչ��

���w������3D

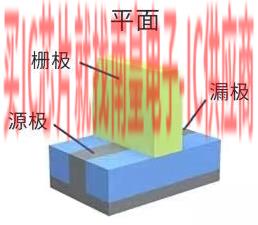

�S�����ϵ�y����Ҫ�����Ǿ��w�ܡ��^ȥ�����w��һֱ���ɾ��w��ͨ���Č��Ⱥ��L�țQ���ľ��w��ͨ���Č��Ⱥ��L�ȡ����w�ܵ������ɷ�����ͨ���ϵĖŘO���ƣ�������ͨ���ܿ��ƣ�ֻ���ṩ���Ŀ��ơ�

��ƽ���D��3D��һ���Ǟ�ͨ���OӋһ�����������������ŘO���ơ�Ȼ�������ˌ��F��ѿ��ƣ���Ҫ���|���w�ܵ��������棬�Ķ����M��ȫ���ŘO(GAA)���w�ܵİlչGAA�ڽY���ϣ�����������Ƭ�ѯB��һ�𣬖ŘO������ȫ������ͨ����

չ��δ����3D DRAM

�S�C�ӑB��ȡ�惦��(DRAM) ����C���c3D NAND��ȫ��ͬ��ʹ�õķ���Ҳ���ˏصĸ�׃��

DRAM����2D���_���������һ�����𡣴�ֱ�ї������y����Ҫ������аl���ҵ������ķ������ѯB늽��|�ͻ��Թ衣��̿�����Ҫͬ�rӰ푶��ӡ���Ŀǰ߀�]�д�Ҏģ���a���^�̡�

3D���bԽ��Խ����

оƬ���b�������ӡˢ�·����(PCB)���^ȥ�����bֻ�Ǟ��˱��o�����Ĺ�оƬ���������B�ӵ��·���ϡ�����bͨ����������оƬ���S�����p��оƬռ�ÿ��g��������ӣ����bҲ�_ʼ�D��3D��

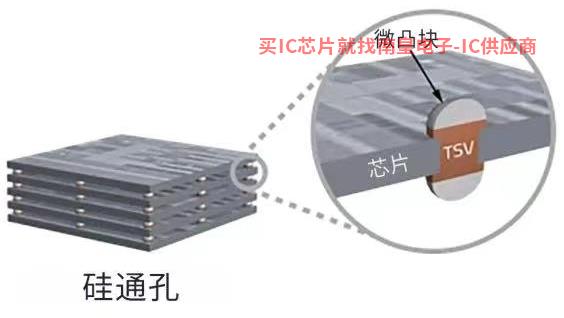

3D���bҪ��оƬ�ѯB���@�漰��оƬ֮�g���ܼ��B�ӡ����@�N�B�ӿ��������̖�ٶȣ��������Ҫ�̵ö࣬���ҿ���ͬ�r��ݔ�������̖��Ȼ�����ڃɂ�����оƬ�Ķї��У�һЩ��̖Ҳ��Ҫͨ�^��ݔͨ���B�ӵ����ߵĶї�оƬ���Q���ͨ��(TSVs)��

3DоƬ�ї��ڃȴ��I�����Ҫ�K���Ј�����-�ߎ����ȴ� (HBM) �@���Ҋ�ġ��ȴ�оƬҲ���Զї���CPU����������߉оƬ�ϣ��Լӿ�ăȴ��Ы@ȡ�������ٶȡ�

���3D���s�ı�Ҫ�l��

���]3D�ѳɞ�˜�������D�����ܲ��ǽ�Q���І��}���x���������������e���á�

ÿһ���µđ��ö����S����Θ����Ć��}���@��Ҫ����˼�S�輼�g�I��Ŀɳ��m�lչ���댧�w�����O����оƬ�ИI�ij��m���FD�Y������Ҫ�Ƅ��ߡ�

- ��һ������Ƭ���f�����h�R������ �ƌW�҂����˺��L�r�g��������Ƭ���_��ʲô

- ���錦���N��Ӱ푼�2021��չ��

- ��˼�Ƽ�����OPPO�����аlоƬȫ�^���OӋ���ṩܛ����ȫ��Q����

- ��˹���Ԅ��{�ˎ��

- 2022�꣬����Ԫ�ǘs�@������֪�R�a��ԇ�c��λ�J�� չʾ���Č������ֳɹ�

- EDA���ҹ����о���������-�A�����EDA���ҹ����о�������ʽ�{����ҹ����о�����

- VIAVI����Rakuten Symphony�������M5G Open vRAN������~�����

- ����500���J�ɰ�ɭ����׃��֮·

- ȥ����ӯ�� ����16.8��

- ��ꐄń�Ħ���_�� Razr 2022:���C�r�g�@ϲ��չ���OӋ�ع�

- ʿ�m���SiC��һ�l�Դ�������a������ͨ��SiC�O��оƬͶƬ�ɹ�

- ����:�����F����̓�M�F�������F��