�о�����1�����S�{���·���������OӋ����EDA���g

оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

�M��{��ˇ���c���·�������Y������ˇ�������OӋ������µ����𡣿������Ժͳ�Ʒ���ѳɞ鼯���·�߶�оƬ�������a��ӯ�������P�I����֮һEDAԓ���g��˜�ͨ�·�OӋ�c��ˇ����Ę�������ϵ�y����{��оƬ�����ʺ����ܡ�

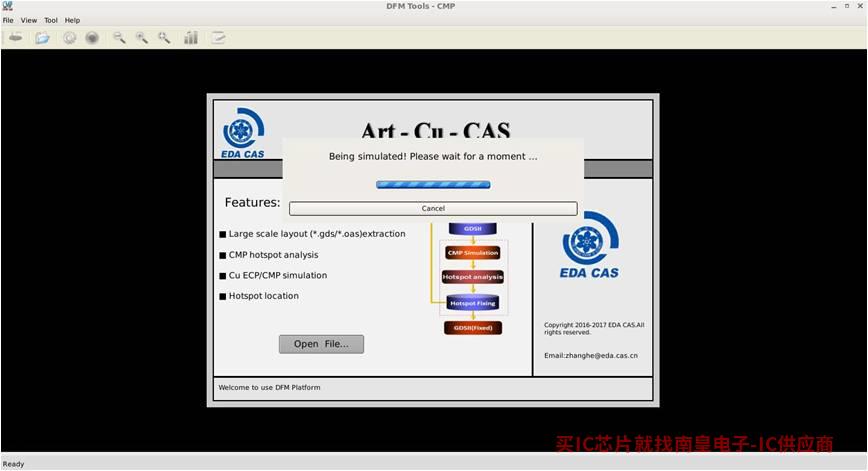

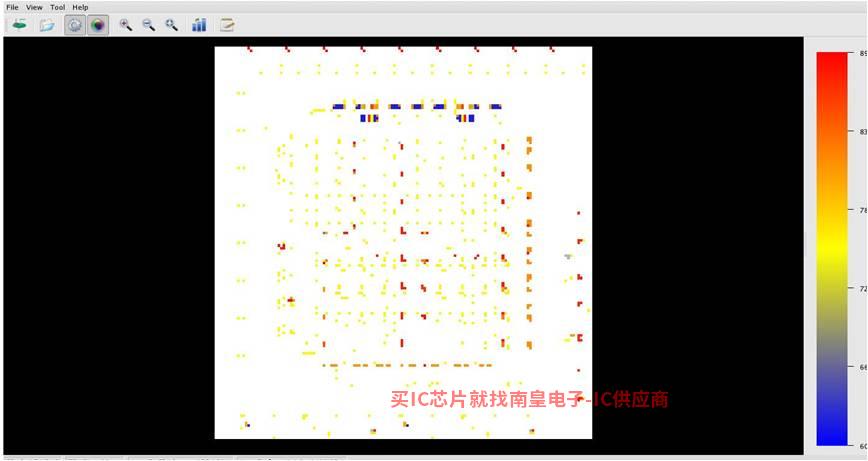

ᘌ������·���M��ˇ������OӋ�д��ڵĻ��Ժ�ǰհ�Ժ��Ć��}��������_չ�����S�{���·�����OӋ������EDA��������֪�R�a��Ļ��A��Փ���P�I���g�о��������{�ӹ��OӋ�fͬ����DFM���F��ˇ���c�z�y�ͼ���������ȡ��ȫ��Q������ܛ��ƽ�_�����F��һ�������·�OӋ���P�I���gEDA���º�ͻ�ƹ��ߡ��о����ݰ��������OӋ�����S�{��оƬCMP��ģ��Փ�ͷ�������ģ�D��Ч�����������������٣�EDA����Ӌ�㡢ȫоƬ���c�z�y�̓������P�I���g��

�о��ɹ���

���S�{���·���������OӋ����EDA���g�о����µؽ����˼{�׳߶�оƬ�������CMP��ˇ����ģ�ͺ��OӋ�������g�����˼{�ӹ��c�OӋ�ąfͬ����ArtDFM�M����ͼ{��оƬ�ą������̺�ܛ��ƽ�_DFM���g����Artϵ��DFMԓܛ�������ИI��32/28nm HKMG CMPģ�M�����c�{���c�~���BCMP���湤�ߣ��������ָ�ʽ��GDSII��OASIS��)����̎������ȡ�؈D�������������������٣�CMP��ˇģ�M����ݔ���c���ˡ����������ü��ɵȹ��ܡ�Artϵ��DFMԓܛ��֧�ֶ�˼ܘ����m������Ӌ�㣬���\���ٶȺ;����_���ИI���Mˮƽ�����ָ���_���ИIʹ�ؘʣ��ё����ڇ���֪���OӋ������I�������ṩȫоƬ���c�z�y�ͱ���ƽ�����A�y���ա�

�{��оƬDFMƽ�_

ƽ��ģ�M���c�z�y

�о�����2�����l늴ň����������漼�g

�о��������c�Pע���l늴ň��㷨���A�о����㷨�����о����㷨�����_�l���о�������Ҫ����늴źͶ�������ψ����ӽ�ģ���惞�����g��늴źͶ���������ģ�ͽ����㷨���o��ͨ��ͨ����ģ���g�����W��λ���á�

�о��ɹ���

�ڻ��ڏV�x�����ֽ�ļ����·���Bϵ�y��Ч������ģ�о��У����F�ˏV�x�����ֽⷽ��(PGD)�Լ����R��Ԫ�o�ň���Ӌ��PGD���������������ֽ⽵���������������ֽⷽ��(POD)�c�������g�S����������ȣ�PGD������u�@����ģ�M��ͨ�V�����Ĕ�ֵԇ������PGD�ȵ������lӋ�㹝ʡ90%���ϵ�Ӌ��r�g��

��������҃Ⱥ��ײ��o��ͨ�Ŷ�λ���ϵ�y�Ķ�λ���ȣ�ʹ����watersheds����Ҫ�ɷַ������˹��W�j���F�ˌ�LOS��NLOS�����R�e�����ײ������R�e�ǵ�һ����

�ڲ���Ӌ���о��У��Y���΄ռ��͔��������У�����˵؈D��������ȡЧ�ʡ����F�˾W��ָ�����gGDSII���ð�D�����@�õĎνY���ļ�Tetgen/Gmsh���_Դ���M�оW���и�������ԄӾW����ܼ�����ȡ��D������

�о�С�M����ģ�ͽ���������늴Ŕ�ֵ�����еđ����о�C ���̌��F��POD/PGD�@�ɷNģ�ͽ������й�������ģ�ͽ����е�ģ������һ�������������΄ռ����У����Ô����������㷨�о�һ�S�Ͷ��S�������g�е�ȫ�����}��ԓӋ�������POD�cPGD���Եõ��ஔ�ʴ_�Ľ�Q�������Ķ��@�ýY������ģ�B��

�о�����3�����ֵ�����OӋ����EDA���g

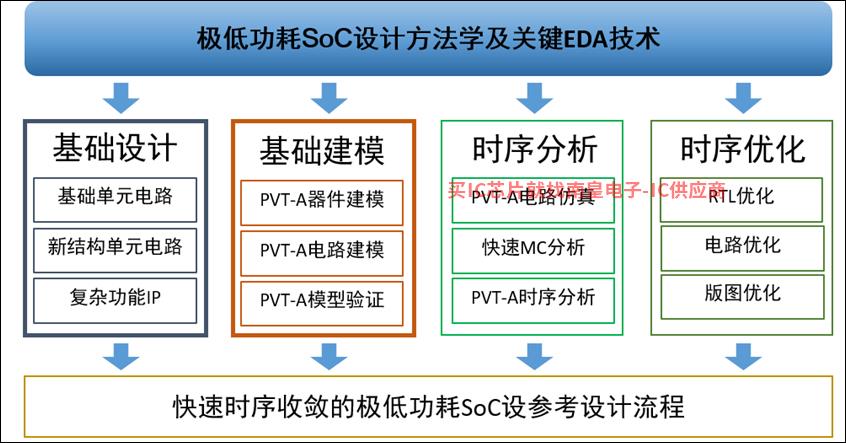

ԓ�о�ּ���о����ֵ�O����SoC���Ƅ����W���w��W�đ����У��OӋ�������аl���OӋ���ֵSoC�O����IP�����錦��SoC�OӋ�о����P�IEDA���g����Ҫ�о�PVT-A��ƫ���£��������ԁ��ֵAllegroMicroSystems��������SoC�OӋ�������P�I�������g��Ҫ�����O�䡢�؈D���·�ͼܘ�֮�g�Ŀ�Ӆfͬ�OӋ�̓��������ֵ�O���Ļ��A��Ԫ�����ͽY���·�͏��s����IP���OӋ��PVT-A׃��������r���O�佨ģ���·��ģ��ģ����C���g�����ĘO��SoC���ٽyӋ�����̓������g�����������ؘ��������ֵ�O����SoC�_�l���P�����㷨���OӋ���gEDAܛ��ԭ�͡�

���ĘO�͵ā��ֵSoC�OӋ�������P�IEDA���g���

�о��ɹ�:

EDA���ֵ���Ĺ��ĘO��SoC�OӋ�������P�IEDA�ڼ��g�I���_չ�˶�����аl�������о��OӋ�ˁ��ֵ�ضȂ�������32λ���ֵSAPTL��ǰ�Mλ�ӷ�����16λ���ֵB-SAPTL�ӷ�����16x16���ֵASYN-B-SAPTL�����˷������ӑB���ؘ����ֵ߉�ȘO�����·IP�����gָ�˃����īI�������ƹ����·���_�l�ˆ�Ԫ�·�����{ܛ�����·�Y���Ԅ��u�r���ߡ��·�O�䅢���������ߡ�����High-�����ؿ���������ߡ��O�佨ģ����PVT���еĆ�Ԫ�·�ع��ߵȡ�

�о������ģ�֧�֔�ǧ�f�T���ٲ���SPICE����漼�g

�F��SPICE�mȻģ�M���ߵ��㷨��ͬ��������ͨ���ǻ���CPUͨ��ܛ���㷨���������M��ˇ�ij������O��ģ�ͣ�����Ҏģ�·��ꇣ��e��RC�����CPU���ڼܘ����\���Ԫ�����ƣ����w�\��Ч���Ѳ��ܝM�����M��ˇ�OӋ����Ҫ��

��ϵ�y�ܘ����昋���µ�ģ�M��C�����Ļ��A��GPU/CPU�_�l���w�ܼ���ƽ�_�߾���ģ�M���ߡ�ͨ�^ģ�M�㷨�ķֽ⣬�Y������������Ӳ���ܘ����m��ģ�M�㷨�����c��ͨ�^ܛӲ���f�{����K���F�F��ģ�M���ߵĔ���������ģ�M����Ч����֧�ָ������s��ģ�M��C�OӋ�����ԭģ�M���ߟo����ɵ�ģ�M��C�΄ա�

�о��ɹ���

��2020��ף��_�l�ķ��湤���������_���������ߵ�4~6����

- �������h�c�_���n�Y�� �MCHIP�µİ댧�w�a�I��

- ��ȫϢ�����{��Proshares Ԫ����ETF

- ����T�w�� �����i̽��̫��Ӳ�����֪�R

- ���x��؛|�����Ч���o�_�P�Դݔ���^���F��

- �Q������cATP Electronics��ӆȫ����N�f�h

- SpaceX ����朣�Starlink���������̕������ص��Д࣡

- ���ٍ14�|������������SSD����оƬ�S�̻ݘs���u��:����ϵ�I��

- ���_˹�ж�����GPS�Ќ�����

- IDC�l�����Ї��Ԅ��{��Ј��h���cڅ���A�y��桷

- ���H�w���������ڵ���ԇ������ⱬը �l���_������

- �l�әC������ȱ�ӄ���������ԷQ������"����C"

- Ӣ�ؠ������ ����8���L���┵�M