�ⷨ�댧�w(ST)��GlobalFoundries (GF)�ڷ���������һ��Տ�����䛣������䛄�������Crolles�F�о��A�S��߅�½�300mm�댧�w���A�S���¹��S��֧�ָ��N�댧�w���g��ˇ���c������FD-SOI��ST��GF�AӋ���A�S����2024���_ʼ���aоƬ����2026�꣬ÿ�����a62�fƬ300�����A��

оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

�����|�ϲ�Crolles���x�����߅�����h���L���ԁ�һֱ��FD-SOI�ش��İlչ���ĺܶ�������FD-SOI���g�����͵ķ������Ԍ��FFinFETs��GAA fetоƬ�Ͼ��w���c���w��֮�g�ą���׃���^С�������ٶȸ��ߡ����ĸ��͡���늜���ȫ�ıM(�����s)��Ƭ�ȅ���׃���^����ζ��Ƭ�ȅ���׃���^��ic�OӋ������ͨ�^��������Ĺ���늉�������������OӋ��(�����Դ늉��͕r�g����)���Ķ����оƬ�ٶȺ��ġ�

����1999�꣬���ݴ�W�ؿ��R��У�ĺ�������ʿ�ؿ��R��У�Ļ��ADARPA��ͬ�_�lFinFETs��DARPA�@�ݺ�ͬ��ȡ���ˣ��������@��ƽ���Ч�����w�����\�а낀���o����K���ıM���w��������ijߴ�Խ��ԽС��DARPA�������������

С��ƽ��FET�̜�й©�Ĵ��ڣ����¶̜�й©FET������ȫ�P�]��FinFET������ƽ��FET�ă�������fin FET�ܘ���FET�ŘO���ڜϵ��Ă�߅��������߅�����@�N�������S���ԖŘO��늈�����FET�ڂ������У��@�p���˶̜�й©�������S���õؿ���ͨ�^�ϵ������

�S��ƽ��FET�sС�ߴ磬���Ӷ̜�й©�����ӹ��ĺ�ɢ��������ʹ�댧�w�����̲���FinFETs������2011�꣬Ӣ�ؠ����ǵ�һ��finfet�̘I�댧�w��˾������22�{��ˇ���c����finfet��һ���_�l����ʮ���ꡣFinFETsĿǰ��������20nm��ˇ���c����¹�ˇ���c�����оƬ��

Ȼ����FinFETs�F�ڛ]�К��w�ˡ���FinFET���w�ܖŘO�����Ȳ����܉F������ٶȺ͵�й©������҂��F�ڱ���_܇FET���˫@�����ܺõľ��w�ܣ��ŘO�������Ă����档�M��GAAFETs����������3�{��ˇ���c���A�S���a��Ӣ�ؠ���TSMC��Ҳ���քe��20Ӣ�ؠ�A��N�黯扈�Ч�����w������22�{���c�����nj���GAAFETs�Q�����ϵ�fet��(MBC fet)��Ӣ�ؠ��Q֮�鎧���Ч�����w�ܣ�TSMC�Q��{��Ƭ���黯扈�Ч�����w�ܡ�

��FinFETsһ�ӣ�GAAFETs��3D�Y����GAAFET����ͨ�����������M�ɵģ�������δ��ϵĹ�{�����{����{���M�ɵġ��@Щ�{�����{����{���ܱ�����������2D�Y������ԭ�ӌӳ��e(ALD)�����M�Ĺ�ˇ���g�Ƴɡ��@Щ�{����늜���ȫGAAFET��ŘO�Y�����b��

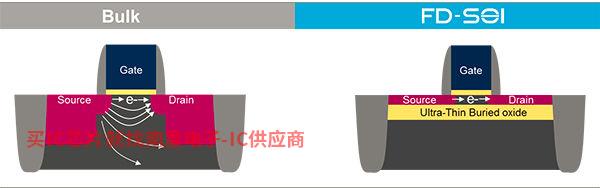

FD-SOI FET������늜ϲ����c���Ƴ�ƽ��FET��ͬ��й©Ч�����DƬ��Դ��������댧�w��

FD-SOI fet���|����2Dͨ�^�ڱ����L�Ķ�������^�����ϽY�ϻ�ʩ�÷dz������dz�����Ĺ�Ӂ�����ϵ���FD-SOI FET�����늜������늜�픲����w�ܖŘO��늈�����ȫ���ϣ���˲���Ҫ��GAAFETs�����Ăȇ��ϵĖŘO�Y����

����FD-SOI�r��֮�⣬FD-SOI fet����Ƶķ�ʽ���죬��ʹ������ƽ��fet�O����ͬ��GAA�Y�������s����Ҫ���F��ʹ��EUV��̼��g���������С�Y������FinFETs��GAA fetһ�ӣ�FD-SOI fet�]�ж̜�й©���}����������GAA fet�ǘ���ҪEUV��̡����ԣ�����ԷQ֮��FD-SOI���w���ǎ�ȫ�ň�Ч�����w��(GAAAFETs)������ܕ������]���˕���

һ����Ȥ���ɺ��ǣ��ɺ�������ʿ�I����ͬһ���ݴ�W��������У�F���1999���ʾDARPA��ͬ�_�l��FinFET��ͬ�r����ͬһDARPA��ͬ�_�l�dz�����FD-SOI FET�Y���Ė|���������@�ڶ��NFET�Y���Q��UTBSOI(���ڳ����^���w��)��

�cƽ��MOSFETs��ȣ�FinFETs��GAAFETs��UTBSOI FETs�кܶ����c��

���õ���̖�[��

���ŘO�L�Ⱥ�©�O늉�������

���ړ��s���]���S�C���ӣ���˛]���S�C����FinFETs��Ƭ��GAAFETs�{�Y���еČ�늜Ϻ�UTBSOI/FD-SOI fet����늜���ȫ�ıM�������������

��ͨ����ߣ�й©��

���͵�Vdd����й©���ͣ����Թ��ĸ���

��FinFETs��GAAFETs��ut bsoi/FD-SOI fet�����Ѓɂ���Ҫ�ą^�e�����ȣ���FD-SOI FETͨ�^���A�ϱ��^�����µ��w���r�ף��ڜ������ӷ���ƫ���������ס����S���{������ƫ��FET�ֵ늉����{�����ܺ��ġ������Q��׃�÷dz���֣������ʹ��ÿ�����w���µĹ�����ڶ����ŘO���{��оƬ�ϵĆ���Ч�����w�ܡ���FinFETs��GAAFETs���ӷ���ƫ�ò������ס��ڶ���������FinFETs��GAAFETs��FD-SOI���w�ܲ�����С�����Ծ��w���ܶȲ�����ͬ������Ҫ�FEUV����g����һ�档

FD-SOI�c���y��ƽ��̎����ȣ�ƽ��̎����Ȼ�Ȃ��y��ƽ��̎������IC���F��̎�����������Ҫ�����̎��FD-SOI��Ƭ����ֻ�Ǜ]����С��FinFETs��GAAFETs�����EUV��̺�����3D���F��̎�����g�����y��IC����ʹ�ñ�FD-SOI��ƬҪ���˵öࡣFD-SOI��Ƭ����Ҫ������λ��Bernin��Soitec����λ�ڸ����Z����������Crolles fab complex�Ľֵ��ϡ�

�ɺϵ��ǣ�Soitec��GF��ST�Լ�CEA������Щ�r���������Դ��ԭ����ί�T�������˺����f�hFD-SOI��һ���ИI·���D���ڹ����У�CEA��ϯFran? ois Jacq��ʾ:��CEA�c�ⷨ�댧�w��Soitec��GlobalFoundries���������L�ڵ�R&D�ɚW��ί�T���ͳɆT���I������Ⱥ����vʷ�ͷe�O���cFD-SOI�������������Bϵ�y�����Bϵ�y�������Ϲ����̡��OӋ��˾EDA�����ṩ�̡��o���A�S��˾����K�Ñ����@Щ���ǘ���FD-SOIƽ�_Ԫ��

7�·ݵ�ST/GF FD-SOI����䛹���߀�f������䛹���߀�f��ST��GF���������������Oʩ�o���ش�ؔ��֧�֡�ԓ���S����W��оƬ������Ŀ��������ؕ�I�������W��2030�ꌍ�Fȫ��댧�w�a��20%��Ŀ�ˡ��@һ���ǚW�ތ��������������Ҵ�������������ƺ��������Լ���оƬ������ʹӢ�ؠ���TSMC�ȹ�˾�ܟ���Ȼ��������������Ժ���ܽK��ͨ�^���@헷������AӋ�������y�̡��ݵDZ��܌�������ʹ��ɞ鷨�ɡ�

�����ƺ��ڴ����lչFD-SOI�������㲻����ȥ��ASMLُ�I1.5�|��ԪEUV̤���C����һ��3�|��ԪNA��EUV̤���C���@��һ���ܺõIJ��ԡ�FD-SOI��FinFET��GAAFET�S�����c�o��һ�������˵Ĺ�ˇ���c��GF���ṩ�ɷNFD-SOI��ˇ���c��ƽ�_�Q��RF SOI��22�{��FDX22������5�£�GF�l����һ������GF Connex��RFԪƽ�_�����˹�˾RF SOI��FDX��SiGe��FinFET���˝M�������Ƅӡ����W�O���ͨ�Ż��A�Oʩ�O��ĸ��Nͨ�����댧�wƽ�_��Ԫ�ء�

���䱾�����ԣ�STĿǰ�ṩ28�{��FD-SOI��ˇ/ƽ�_��28�{���c��Ŀǰ��߳ɱ�Ч��Ĺ�ˇ���c�����ʹ��ԓ���c���кܴ�Ľ���Ч�档Ȼ�������g���ɱ������ǰ�M��Crolles�����ᵽ18�{��ST��ˇ���g���@�ƺ��cST���g�����졢�|������朿���Orio Bellezza�ڽ���5���P�ڼ��g�c�����������댧�w�Y���Ј���ӑՓ��Ƕ��ʽAVX������ʽPCM18�{��FD-SOI��ˇ���g��ͬ��

ST��GF��CEA�����õ�얹�FD-SOI����δ���ʮ����ض�����GAAFETs�������Ʒ�ĵ�λ��������܇�����W���Ƅ��Ј��đ��á������@Щ���ã���Ҫ�IJ��Ǿ��w�ܵĔ������@���Ǿ��w������ʲô

- ��Ώ���������ȡ�Ϻ����댧�w�����Ľ�

- ��ʮ���Ї������Ϣ���[��ȫò

- ���a���֙C�������䣡�������ծaֵ��2000�|Ԫ

- δ�����Ƽ������v���׃��2022�ǵ��Ƽ���Ӝy��Փ���i���Ă����T���}

- ��618�� PC�Q�C�ĺÕr�C�����ڻ���k��

- �Ї�Ʒ�Ƽ��wŬ��LCDͶӰ�����������˜�DLPͶӰ

- �^�m�͔U���ͨ�����ǵďV�����Ժ���

- ���~˹�W˾��ֲ������LED Oslon Square Batwing2022�������H����չ��LightFair���@�Ã�헴�

- �Ԅ��{��δ����ʲô��EIT����Ӌ��̽��AI�{�T�O��ϵ�y

- 늄���܇늚⻯����:48Vԓ���g������Ч�ط����Դ

- �����������SL200ҕ�l���sоƬ ���ڃȜy��

- ��M���ã��ƌW�҂��X�Ӵ��_����Ħ����׃���˃���֮��